# Development of On-Board Embedded Real-Time Systems: An Engineering Approach

TULLIO VARDANEGA

Copyright © T. Vardanega, 1998

DEVELOPMENT OF ON-BOARD EMBEDDED REAL-TIME SYSTEMS:

AN ENGINEERING APPROACH.

### 1st edition (August 1998):

As doctoral thesis presented at the Technical University of Delft (NL).

Approved on October 6, 1998 by the following exam board:

Prof. O.J. Olsder, Technical University of Delft, chairman.

Prof. J. van Katwijk, Technical University of Delft, promotor.

Prof. A. Burns, University of York, (UK).

Prof. H. Koppelaar, Technical University of Delft.

Prof. J. Zalewski, University of Central Florida (USA).

Prof. J.-A. de la Puente, Technical University of Madrid (E).

Prof. H. Sips, Technical University of Delft

for Prof. F. Panzieri, University of Bologna (I).

Dr. W. Toetenel, Technical University of Delft

for Prof. K. De Vlaminck, Catholic University of Leuven (B).

### 2nd edition (November 1998):

As technical report for publication by the European Space Agency Research and Technology Centre (ESTEC) at Noordwijk (NL).

# **Chapter 4**

# An Evolutionary Approach to the Construction of New-Generation Systems

# 4.1 Introduction

This chapter combines the components of the engineering strategy outlined in chapter 3 into a comprehensive approach to the development of new-generation on-board embedded real-time software. In the remainder of this work, chapter 5 and 6 will demonstrate the operation and fitness for purpose of our concept.

The discussion in this chapter covers an extensive amount of material, which spans from the conceptual description of the proposed development model up to the definition, implementation and characterisation of the associated enabling technology.

The structure of this chapter is as follows:

- a. Section 4.2 introduces our revisited interpretation of the PSS-05 development model, illustrates its focus on the support for the iterative and incremental consolidation of the real-time structure of the system (i.e. the physical model) relates it to other known and relevant innovative approaches and summarises its overall rationale.

- b. Section 4.3 describes the structure and organisation of development activities in the process and identifies the requirements on the associated enabling technology.

- c. Section 4.4 provides an overview of the design method which we have adopted as the centre of our engineering approach.

- d. Section 4.5 presents the technology that supports our iterative and incremental approach to design, implementation and static analysis of new-generation systems.

e. Section 4.6, finally, relates the projected benefits of our approach to the known limitations of current practice.

# 4.2 Methodological Approach

# 4.2.1 Outline of the Proposed Approach

Earlier in this work, we have seen that new-generation satellite systems will be increasingly soft-ware-intensive and confronted with the urge to dramatically compress the associated development schedule. With software becoming central to the implementation of such systems, the suitability of the current software process and associated support technology needs to be reconsidered in the light of the emerging requirements. This was in fact the main object of chapter 3.

Section 1.4 had anticipated the strategic line of our work and argued that the future software development process ought to be turned, from the classical waterfall model, into an *explicitly iterative* and *incremental* process. This is an essential component of the productivity boost required to cope with increased software complexity in the context of a dramatically compressed development schedule. The value of this strategic component was in fact advocated by chapter 3.

In anticipation of the increasingly concurrent and time-critical component of new-generation systems, section 1.3 had also called for a more effective development paradigm capable of mitigating the labour intensiveness of the real-time verification activities. Chapter 3 placed special emphasis on this particular aspect and outlined the essential ingredients of the desired evolutionary solution. In particular, chapter 3 highlighted one major deficiency of the PSS-05 development model [ESA, 1991] in the respect of time-critical systems. In fact, the PSS-05 model, which currently informs the software development practice of European space industry, fails to recognise that an important proportion of the real-time requirements on on-board software systems arise as *second-order* requirements in conjunction with the establishment of the physical model of the system. The PSS-05 model requires that the requirements capture feed into but be kept separate from the establishment of the physical model. This approach is therefore exposed to the risk that second-order requirements may escape the elaboration and analysis destined instead to all the first-order requirements captured in the SR phase.

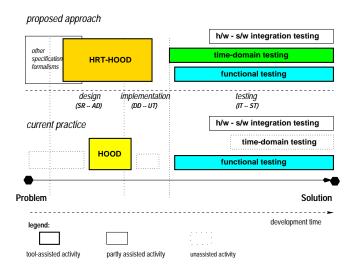

The lack of explicit support for the capture and analysis of such an important baggage of requirements implies that no comprehensive verification of the system concept can effectively be carried out in the descending branch of the V-shaped PSS-05 development model (i.e. the design and implementation phase). This deficiency causes the *entire* burden of verification to be deferred to the ascending branch (the testing phase) only to result in the transfer of an improper extra load to the IT—ST segment of the process shown in figure 3.1. Section 3.3 discussed this phenomenon and nicknamed it the "snow-plough" syndrome.

The effects of the snow-plough syndrome are particularly antagonistic to the required reduction of the development schedule. Any significant result in that respect, in fact, cannot be obtained other than by decreasing the effort and complexity demanded by the testing activities, which often take up to 60% of the overall development effort. In our interpretation, this essentially means that the IT—ST segment must be offloaded of concerns which can be resolved earlier in the process.

It is apparent that, in the face of the anticipated reduction of the development schedule, the level of effort devoted to the testing phase cannot increase proportionally with the increase of the real-time complexity of new-generation systems. In view of this, section 1.4 and 3.4.2 have proposed to replace as much *late* dynamic real-time testing as possible by a functionally equivalent amount of static real-time analysis performed *earlier* in the process, as a remedy to the ill-balancedness of the present effort distribution across the life cycle.

As discussed in section 3.4.3, we want to achieve this objective by introducing two distinct enhancements to the current software process, namely:

- (1) The notion of Computational Model (introduced in section 3.4.4), as the means to augment the expressive power of the design definition phase to capture: (a) the real-time attributes and execution characteristics of the components from which the software system will be constructed; (b) the real-time execution model which underpins the design of the system; and (c) the means of communication and synchronisation applicable among components and between them and the external environment.

- (2) The introduction of a unified *design framework*, to embrace the activities of the descending branch (i.e. requirements analysis; design definition; design analysis and implementation) into a single, unfractured development phase within which they can proceed in an *iterative* and *incremental* fashion and ordinately respond to the *feedback* arising from the progressive consolidation of the system.

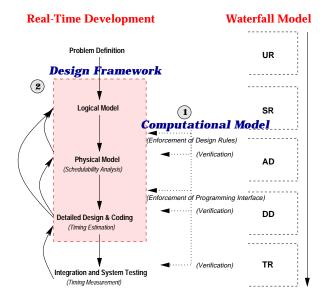

Figure 4.1: The Proposed Software Process.

Figure 4.1 illustrates our development model and contrasts it with the conventional waterfall approach.

The figure shows: (a) the *design framework* (the dashed box tagged with a (2) in the figure) which embraces the feedback-based development iterations occurring within the the SR—DD segment of the V model along with the consolidation of the system concept; and (b) the notion of *Computational Model* (tagged with a (1) in the figure) which supports the establishment of the physical model, the adoption of conforming design rules and implementation choices (denoted by the left-headed arrows tagged "enforcement" in the figure) and successive and incremental stages of static timing analysis (denoted by the left-headed arrows tagged "verification" in the figure).

As the figure portrays, our process concept is geared towards the capture and accommodation of the design and implementation iterations caused by the feedback from requirements consolidation and / or timing analysis. The *design framework* is the structured development space in which such feedback can be analysed and responded to by design and / or implementation refinements. The *Computational Model* is instrumental to this objective, for it allows the real-time issues to be captured at the design level, coherently transformed into a conforming implementation and statically analysed at all stages of development.

Section 4.3 will build on this initial concept in the definition of the process model that this work wants to promote.

# 4.2.2 Relation to Other Development Approaches

The basic rationale of our development approach originates from the same motivations which underpin the design methodology advocated by Fohler and the MARS team in [Fohler et al., 1990]. The goal of Fohler et al. in the cited paper is to propose a design methodology (seen as a collection of complementary development methods and the relevant use rules) specifically suited for the construction of time-critical systems. Fohler et al. argue that the construction of real-time application software which does not consider the characteristics of the target system is totally inadequate. The cited authors also insist that the consideration of time must form an *integral part* of the design methodology, from the initial requirements definition down to the implementation level. Fohler et al. maintain that time must be represented in a *uniform and concise* way all along the development process. Finally, the cited authors advocate the need for means capable of supporting the *early evaluation* of the design with respect to its timeliness requirements.

In fact, our work departs from that of Fohler et al. in the respect of technical choices made to respond to the same core of identified needs. Kopetz in [Kopetz et al., 1993] outlines the implementation approach taken by the MARS team in accord with the cited work of Fohler et al. In contrast with that approach, our work acknowledges the occurrence of feedback-based development iterations across a greater portion of the process than the Kopetz approach allows and builds on them for the incremental consolidation of the system.

Our approach has also much in common with some of the views expressed by Kruchten in [Kruchten, 1995]. According to Kruchten, common experience has it that the description of a software architecture is not necessarily well served by a single architectural style. No single style, in fact, is normally capable of providing the "right" type and amount of information to all

members and functions of one development team. There may exist as many styles of expression as the viewpoints that can be taken with respect to the software architecture as a product. Kruchten voices this evidence and proposes a model which contemplates four concurrent views to describe the same software architecture and one common space in which the various views can come together through the illustration of selected use cases or scenarios. Kruchten recognises the co-existence of: the logical view, to describe the functional behaviour of the system; the process view, to describe the concurrency and synchronisation aspects of the system operation; the physical view, to describe the topology of the system architecture; and the development view, to describe the static organisation of the system components in the development environment. Kruchten allows each view to have its own notation and be expressed in terms of the set of architectural elements, representations and associated rationale and constraints that suit the development perspective. Kruchten also advocates an iterative development in which the architecture is prototyped, tested, measured, analysed and refined in subsequent iterations. Kruchten claims that this is better suited for ambitious and unprecedented projects — for which too little is known at the end of individual phases to validate the architecture — than the conventional linear approaches which contemplate backtracking merely as an exception.

Of the four views advocated by Kruchten, we are not interested here in the physical and the development views, but we have clear parallels between his logical view and the PSS-05 logical model and his process view and the PSS-05 physical model. We contend, however, that the architectural notation used to describe the physical model can be based on the same, yet enhanced conceptual framework used for the logical model. We argue that this provision simplifies the transitions and iterations between the two.

### 4.2.3 Rationale of the Proposed Approach

The operational correctness of real-time systems needs to be verified in the *value* domain as well as in the *time* domain. The latter concern demands that attention be paid to the constraints and properties of execution on the run-time environment which may effect the time-domain behaviour of the system (e.g.: hardware architecture, clock frequency, means of communication with the external world).

For embedded real-time systems in general and on-board systems in particular, the nature of the execution environment not only effects the time-domain behaviour of the system but also plays a crucial role in the determination of its structure and operation. The most part of modern real-time systems use run-time executives or operating system kernels to hide the properties and constraints of execution on the run-time environment into an abstract "presentation layer" offered to the application components.

As a reflection of this basic engineering principle, real-time systems are normally structured in the classical layered fashion. Consequently, the application components execute on top of a runtime executive and are designed around the services, means and abstractions that the executive provides.

Hence, the structure of applications in this domain is determined, to a great extent, by the need to fit the abstractions and execution model supported by the run-time executive of choice.

This need obviously spawns a set of additional requirements on the transformation of the *logical model* of the system, as seen by the PSS-05 model discussed in chapter 3, into the *physical model* submitted for implementation. In order to denote their derivative origin, these additional requirements are normally referred to as *second-order requirements*.

As opposed to first-order requirements, which directly originate from interpretation of the user specification, second-order requirements emanate from design decisions which are autonomously made by the design authority. Irrespective of their differing origin, though, both complements of requirements equally determine the design of the system and therefore call for equally accurate verification and verification.

The above concern was captured by section 3.3.1 and formulated as follows:

**A.1** In the development of real-time embedded software, a considerable amount of second-order requirements is incrementally defined in conjunction with the progressive establishment of the physical model of the system.

Hence, the timely consolidation of *all* of the requirements which effect the design and operation of the system — which is *central* to the stability and cost-effectiveness of the overall development — critically depends upon the timely establishment of the physical model.

In response to this concern, section 3.3.2 has asserted that:

**A.2** The establishment of the physical model is greatly facilitated by the explicit and consistent utilisation of a suitable Computational Model as the means to structure and automate the verification of the operational correctness of the system in the time domain.

The concept of Computational Model was introduced in section 3.4.4 with the aim to capture and formalise, as *explicit design drivers*, the properties and constraints which determine the execution model of a real-time application.

Assertions **A.1-A.2** are central concerns to the conception of the software process advocated by this work. We now want to refine the formulation of these assertions in a fashion which better reflects the logic of the process which ensues from them:

- **A.1.1** The establishment of the physical model of the system proceeds in conjunction with the *incremental* capture, refinement and formalisation of the second-order requirements which complement the set of direct requirements established with the SR phase of the V model.

- **A.1.2** The introduction of second-order requirements may give rise to important amendments and refinements to the design of the system as determined from the logical model.

- **A.1.3** The development process which ensues is inherently *iterative* and *incremental* as a reflection of the progressive consolidation and verification of the physical model and its impact on the original logical model.

- **A.2.1** The consistency and productivity of this process are greatly facilitated by the explicit *selection* and *enforcement* of a suitable Computational Model and the systematic *verification* of satisfaction of the required properties and constraints.

Hence, in order to achieve the research objectives set forth in section 1.4 in the light of the above assertions, we need to establish a software development process which:

- **C.1** Make of selection, enforcement and instantiation of an appropriate Computational Model an explicit and integral part of the design process, so that definite rules and means for system verification in the time domain can be effectively applied well ahead of integration and system testing.

- **C.2** Cater for automated, incremental and iterative verification of the feasibility in the timedomain of the current design since as early in the development as possible, so that every such step of verification contributes to offload this concern from the effort and complexity of integration testing.

- **C.3** Provide support for immediate analysis of the effect of modifications, enhancements and adaptations to the system which may result from late consolidation of requirements, late occurrence of timing problems, need for in-flight modifications, etc., so that the development process may become more controllably iterative and incremental and therefore achieve the increased internal parallelism which is essential to compress its duration;

- **C.4** Be efficiently implemented using practicable enhancements to the HOOD and Ada technology presently in use, so that its introduction can effectively be as smoothly evolutionary as prescribed by section 3.3.

Each of the above-stated properties originates from assertions, requirements and assumptions made at various points in the preceding chapters. In order to help the reader form an overall picture of the mutual dependences between such arguments, table 4.1 traces requirements **C.1-C.4** back to their originating motivation as presented in this technical report.

| Tuble 1.1. 6 verview of Briving Requirements. |                                     |                         |  |

|-----------------------------------------------|-------------------------------------|-------------------------|--|

| Required Property                             | Justification                       | Origin                  |  |

| C.1                                           | assertion A.2.1                     | sect. 1.4 & sect. 3.3.1 |  |

| C.2                                           | assertion A.1.1-3                   | sect. 1.4 & sect. 3.3.2 |  |

| C.3                                           | requirement <b>R.1</b> , <b>R.3</b> | sect. 1.4               |  |

| C.4                                           | strategic decision                  | sect. 3.3               |  |

Table 4.1: Overview of Driving Requirements.

This technical report maintains that one feasible instance of a development model capable of adequately satisfying such properties can indeed be instantiated and enacted with conventional, yet enhanced, PSS-05-based technology, in keeping with the required evolutionary approach. Yet, no instance of PSS-05-based development model known to the author of this technical report (e.g.: [ESA, 1992b], [ECSS, 1997] and other industry-own standards in Europe) appears to exhibit enough of the required properties.

The constituting elements of the proposed solution, which have been outlined in section 4.2.1, are discussed in detail in the following.

# 4.3 Supporting Concepts and Technology Requirements

# 4.3.1 Essential Elements of the Proposed Solution

The strategic decision discussed in section 3.3 requires that the proposed process amendments be introduced in an *evolutionary* fashion. We show in the following that this can be accomplished by introducing a limited number of enhancements to the HOOD [HTG, 1993] and Ada [ISO, 1987] technology which presently constitute the pillars of the software technology in use at European space industry (cf. e.g.: [Ratcliffe, 1995]).

In particular, we contend that the methods and tools required to support the proposed development model can be constructed along the following directions:

- a. The introduction of a few definite enhancements to the HOOD method, aimed to augment the conventional design process with the *expressive power, constructive guidelines and* verification means provided for by the Computational Model of choice.

- **b.** The implementation of the selected Computational Model upon a *restricted form* of Ada 95 tasking [ISO, 1995], in accordance with the fixed priority preemptive scheduling model selected as the preferred model in section 3.4.6, in a fashion which:

- suits the type of applications to be found in the reference domain (cf. chapter 2);

- is *directly* supported by the recent revision of the language standard.

- **c.** The definition and integration of the enabling technology for the support of: (1) the *advanced verification* of the feasibility in the time domain of the physical model of the system as well as (2) the effective deployment of *feedback-based iterative design*.

As discussed in section 4.2.1, item **a.** and **c.** above represent *essential* enhancements to the current software process. Enhancement **b.**, on the other hand, is an *arbitrary* corollary motivated by our decision to retain Ada as the reference enabling technology.

The *design framework* shown in figure 4.1 is the core of the process model we envision. We now want to define the break-down structure which implements that process in an evolutionary fashion and determine the flow of activities that are to occur within it.

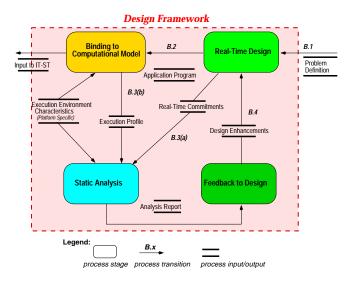

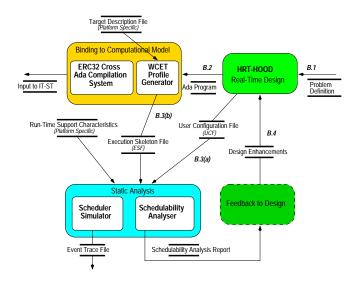

The development activities within our design framework revolve around the four main stages depicted in figure 4.2, as follows:

**B.1** *real-time design*: this stage of the process is initially entered with the definition of the problem as determined by the system specification (i.e. the user requirements); this stage encompasses the definition of the logical and the physical model of the system and focuses on the characterisation of the real-time attributes (commitments) required of the individual components of the system; the activities at this level are supported by the use of an enhanced version of the HOOD method;

58

Figure 4.2: Design Activities in the Proposed Process.

- **B.2** binding to Computational Model: this stage of the process is entered at all times the abstract design of the system is submitted to implementation; at this point, the application program corresponding to the current level of design is automatically extracted from the design tool and fed to the designated compilation system; the compilation system binds the program to the selected Computational Model (thereby ensuring the use of the appropriate programming interface) and determines the processing requirements associated with the worst-case execution time (WCET) profile of the application components;

- **B.3** *static analysis*: this stage of the process is entered to statically determine whether the current implementation of the system is capable of meeting the real-time commitments of the corresponding specification when executed on the designated target platform; at this level, we perform static response time analysis upon a stylised representation of the system and associated real-time attributes, as derived from the current design (**B.3(a)** in figure 4.2) and the WCET profile of the relevant program, as generated by the compilation system (**B.3(b)** in figure 4.2);

- **B.4** *feedback to design*: this stage of the process is entered to review the results obtained from the earlier stage of static analysis and determine the corrective measures (if any) required to ensure that the system implementation meets the designated real-time requirements; the determinations established at this level are then fed back to the design level in order for the designer to keep current the actual real-time attributes of the system and either conclude the design process or perform further steps of design (and / or implementation) increment and corrective iteration.

The process model outlined above assumes a design method which supports the construction of a real-time system in terms of the abstractions, execution characteristics, usage rules and constraints defined by the Computational Model of choice (cf. B.1). For systems designed in this manner, the implementation effort is comprised of two complementary activities (cf. B.2): (a) the derivation of the *concurrent structure* of the system, which is obtained by transformation of the structural components of the design into the corresponding code structures, as required by the adopted implementation of the Computational Model; and (b) the incremental production (by hand-coding or other means) of the functional components of the system and their insertion in the relevant structural element. At any stage of this development process, the system thus constructed is comprised of: (i) the real-time requirements to be met by the system (cf. **B.3(a)**); (ii) the execution profile of the system corresponding to its current concurrent structure and the timing measurements or estimates for its functional components (cf. **B.3(b)**); and (iii) the timing characteristics of the execution environment. This information base is used to perform static analysis of the real-time feasibility of the current version of system. The results of this analysis are reviewed by the engineering authority. The relevant deliberations are then fed back to the design level either to leave the design process (and enter the subsequent phase of testing, as shown on the upper-left corner of figure 4.2.1) or to iterate over the corrective consolidation of the design and implementation (cf. **B.4**).

The implementation of each of these stages of development will be illustrated in chapter 5 by means of a simple demonstrative example. Section 4.3.2, in the following, instead discusses the technology requirements for the implementation of the proposed concept.

## **4.3.2** Technology Requirements

Section 4.2.1 has introduced the evolutionary amendments to the current software development practice which are required to support the process depicted in figure 4.2. In the following, the three main constituents of the proposal (identified as enhancement **a.-c.** in section 4.3.1) shall be presented and discussed in isolation.

### Selection and Enforcement of Computational Model

Enhancement **a.** calls for the introduction of definite enhancements to the HOOD method aimed to augment the conventional design process with the **expressive power**, **constructive guidelines** and verification means provided for by the Computational Model of choice;

The use of the HOOD design method, as presently defined, does not require nor prescribe nor even support the selection, enforcement and verification of any given Computational Model. A HOOD design, in fact, is *static* in that it establishes the functional and operational interfaces between objects without being equally prescriptive on the *dynamic* aspects of the execution of the system. The HOOD method only allows for a *loose expression of concurrency* (i.e. the "control view" required to describe the overall control structure of the system) which, on the contrary, ought to be regarded as one fundamental ingredient of the design of modern on-board systems.

In HOOD, basic rules exist for the designer to determine how threads of control are allocated

to individual objects, but no binding prescriptions are formulated to dictate the rules governing their concurrent execution at run time. In fact, this lack was rather deliberate, for the designers of the HOOD method opted to trade prescriptiveness for generality.

Two components of the method may be used to express constraints on the execution model of the system: (1) the *protocol constraints*, which govern the interaction between the object requiring a given constrained service and the object providing it (cf. section 3.2.2 for a discussion of the basic protocols); and (2) the *object control structure*, which is the design structure intended for the user to express the constraints placed on the control behaviour of the object. The very existence of protocol constraints on an object's operation determines the *active* status of that object. The definition of active object does in turn assume the possession of own threads of control. Hence, active objects are intended to execute concurrently. Yet, no other means than the two mentioned above are provided to express the desired properties of the concurrent execution of active objects.

Even in the absence of a rigorous definition and explicit support for the determination of the execution aspects, however, the design of an on-board real-time control system *always* eventually entails the coupling between the application components (i.e. the HOOD objects) and the execution platform. This necessity should take to the foreground the constructive elements of the Computational Model of choice. More frequently, however, this step is limited to mechanically forcing the needed run-time bindings into the application, with only late consideration given to the real-time properties of the concurrency model imported with the run-time executive of choice.

This phenomenon denotes two important deficiencies of the typical development approach: (1) the lack of effective means for the early enforcement and verification of the required real-time behaviour of the system, which is clearly not addressed as a concern of the design level; and (2) the divorce of the architectural design process from the concepts and abstractions which emanate from the execution platform.

These deficiencies may incur onerous consequences, especially at the critical boundary between the design and the coding phase. They may in fact often result in the loss or decay of such important properties as:

### • design integrity

when components, services and interfaces provided by the underlying run-time system (that is, the incarnation of the chosen Computational Model) are not designed, modelled nor verified with the same degree of accuracy or detail as demanded for the application software;

### • functional cohesion

when requirements arising from the selected Computational Model introduce system partitioning criteria which effect the structure of the system as established in the design phase; this is, for example, the case when the need to allocate system activities to fixed cyclic execution slots introduces a system breakdown structure which differs from the one committed at the end of the design phase (note that, with fixed cyclic scheduling, this case normally occurs as late as at integration testing, when the time-to-completion pressure is typically so high that the required structural changes to the system are treated *locally* at the code level without returning to the design level);

• verification coherency

when the verification of the correct execution of the system on the adopted Computational Model is not performed as part of the design verification but is deferred until integration testing.

In our reference scenario, the core of the design process is carried out by use of the HOOD method. We therefore devise and introduce enhancements to the method which can instigate an *explicit* process of selection, enforcement and binding with the desired Computational Model.

We do maintain that the definition, implementation and enactment of the required enhancements is in fact possible and economically achievable. Section 4.3 presents the proposed solution.

### Predictable and Characterisable Concurrency

Enhancement **b.** calls for the implementation of the selected Computational Model upon a **restricted form** of Ada 95 tasking [ISO, 1995] in a fashion which: (i) suits the type of applications described in chapter 2 and (ii) is directly supported by the recent revision of the language standard.

Chapter 1 has asserted that new-generation on-board systems are increasingly concurrent and time-critical. Chapter 2 has shown that the control activities to be performed by such systems exhibit a broad variety of execution requirements. Hence, the Computational Models for use in the construction of such systems should desirably support flexible and predictable forms of concurrency.

The decision to adopt an evolutionary approach to the amendment of the current software technology raises the obvious question as to how well Ada positions itself with respect to such demands. The question is particularly intriguing in that, in contrast to the vast majority of the most commonly used implementation languages (Fortran, C, C++) the definition of the Ada language embodies the elements of a preemptive priority-based (PPB) Computational Model.

The definition of the Ada 83 tasking model [ISO, 1987], however, was admittedly too broad and general and exhibited several important shortcomings (e.g.: bulky heavy-weight implementation, exposure to priority inversion problems) which made it inadequate for usage in space systems as well as in the vast majority of other high-integrity systems.

Because of such a distinct baggage of deficiencies, Ada 83 was solely employed as a plain procedural language provided with custom-made bindings to the run-time executive of choice.

The divorce from the standard run-time environment of the language and the strategic need for every system builder in the business to possess in house the elements for ready-made custom solutions gave rise to the birth of several differing implementations of run-time executives intended to support Ada-based real-time on-board systems. The short-sightedness of most commercial competitors, however, caused those endeavours not to join forces with major international standardisation initiatives, such as, for example, the Catalog of Interface Features and Options (CIFO) proposed by the Ada Run Time Environment Working Group under the auspices of the ACM [ARTEWG, 1991] and, to a lesser extent, [ExTRA, 1994]. Not surprisingly, those industrial efforts invariably resulted in proprietary implementations, which were *local* (i.e. non-standard across company boundaries) and *semi-formal* (i.e. hardly described in terms of any proper Computational Model).

One common characteristic of those proprietary developments was the generalised rejection of the Ada 83 run time system along with its tasking model. In spite of this, however, some restricted form of PPB scheduling built around custom run-time environments progressively started to appear and be used in an increasing number of space applications. The proprietary executives described in [Matra Marconi Space and GSI-Tecsi, 1990], [MBB, 1991] and [Saab Ericsson Space, 1996] are amongst the most notable examples of this trend. We read this as a reflection of the distinct demand for flexible ways to model the *inherent concurrency* of the on-board processing activities.

Building on this evidence and along the line of argument initiated by [Locke, 1992] and subsequently developed by [Burns and Wellings, 1995a], we argued in section 3.4.6 that compelling reasons now exist to re-consider the suitability of the amended Ada 95 tasking model [ISO, 1995] for new-generation on-board system. This choice would buy the designer the ability to build on-board embedded real-time applications directly upon an international standard instead of upon custom-made variants. In particular, section 3.4.6 maintained that a Computational Model based on the deadline monotonic fixed priority preemptive scheduling paradigm embodied in the Ada 95 run-time support suits well the emerging requirements of new-generation satellite systems discussed in chapter 1 and the inherent characteristics of platform applications highlighted in chapter 2.

Section 4.5 will take this argument further and will demonstrate that we can define, implement to maximum efficiency and fully characterise the Ada run-time support suited for the exploitation of our Computation Model.

### Support for Feedback-Based Iterative Design

Enhancement **c.** calls for the definition and integration of the enabling technology for the support of: (1) the **advanced verification** of the feasibility in the time domain of the physical model of the system as well as (2) the effective deployment of **feedback-based iterative design**.

One distinctive property of the our approach stems from the aim to translate the *design frame-work* concept introduced in section 3.3.2, to a practicable paradigm of development, centred around the explicit recognition of the *iterative* and *incremental* nature of the design process and the ability to provide direct support for it.

The goal is, in this respect, to enable the need for the design iterations shown on the left-hand side of figure 4.1 to arise — and, to some extent, be promoted — *under the assistance and guidance* of support tools tightly integrated with the design process.

The central concept is, thus, for the designer to be able, at several points of the development process (and ideally, as early as during the establishment of the logical model) to obtain prediction, confirmation and verification or otherwise of the correct timing behaviour of the current physical model of the system. This would allow the definition and implementation of any necessary corrective actions to initiate well before the point in time when their impact and cost may become intractable.

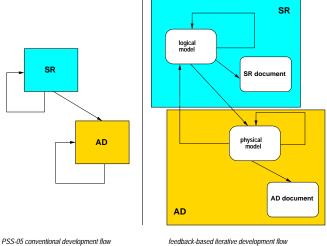

It is obviously important for the overall economy of the development that such an iterative development concept place *within* the normal design process as opposed to *without* it; which, in a

sense, blurs the separation which the PSS-05 standard introduces between the SR and AD phase, as shown by figure 4.3.

Figure 4.3: Feedback-Based Iterative Design Flow.

The realisation of such a concept requires the ability to extract from the current design sufficient information for successive stages of (schedulability) analysis to be performed and continually feed back to the design process.

The nature of the information required to perform such an analysis is manifold and depends on the actual type of scheduling analysis which one wishes to adopt. In general, however, one portion of the required information may directly emanate from known requirements on the current design (e.g.: period, deadline, precedence activation constraints, functional and operational dependences such as those expressed by the "use" relationship in HOOD) whereas another portion shall necessarily require knowledge about the execution performance (represented by the relevant WCET profile) of the code presently or expectedly associated with the design.

Obviously, as the design evolves and consolidates, so do the stability and solidity of the extracted information. Hence, the need to enable this process to be iteratively repeated with the progress of the development requires the ability to progressively replace initial timing predictions with actual measurements based on the code being produced.

### Limiting Factors to Achievable Innovation

It should be apparent to the reader that, in the face of the wealth of the possible technology advances which might arguably meet the demands discussed in chapter 1, this technical report has opted to set forth on a comparatively modest rate of innovation.

The reason for this resides with the need for any proposed technology innovation to negotiate

64

with the non-technical factors specific of the industrial domain, which tend to set tight bounds to the achievable extent of innovation. And this is particularly the case of such industrial domains as the space industry in Europe, characterised — until the present moment —, as discussed in chapter 1, by very specific technical needs and rather modest margins of investment, which justify the option in favour of the evolutionary approach discussed in section 3.3.

Even within a moderately evolutionary scenario, however, non-technical considerations may play a ponderous role. It may, thus, be anticipated that the relative merit of the propositions put forward by this technical report shall be scrutinised by the intended user community not solely from a technical stand-point. This is likely to be the case with the requirement for enhancement **b.** in particular, which may constitute one of the main *cultural* obstacles to the general acceptance of the overall proposal presented in this work.

The anticipated issue has the following two facets: in recognition of the anticipated increase with the event-driven and concurrent nature of new-generation software-intensive satellite control systems, the formulation of enhancement **b.** maintains that the desired Computational Model for use in such systems should be based upon fixed priority preemptive scheduling and hence employ a restricted form of the Ada 95 tasking model.

This proposition, however, places in striking contrast with the commonly-held view that on-board control systems must be strictly *deterministic* in order to be *predictable* (where the term "deterministic" is used to denote a system in which the execution sequence of its components is completely predetermined and fixed for the entire operation of the system, as opposed to the potential non-determinism of fixed priority preemptive scheduling systems).

The contrast between these two forms of scheduling is dated and certainly not exclusive to the space domain. Once deprived of its deprecated "religious" connotations, though, this contrast has resolved, in numerous application domains (e.g.: avionics, car industry, process control) into a fairly straightforward pragmatic design decision, normally made in full awareness of the relative pros and cons of either option. As a result of which, an increasing number of moderate-criticality applications have successfully transitioned to the use of preemptive scheduling.

Papers like [Locke, 1992] have greatly contributed to clarify that, whereas real-time systems "must be capable of providing a *provable prediction* of the ability of their design to meet all of its timing requirements" — whence the term predictability —, *determinism is, indeed, sufficient for predictability but not necessary to achieve it.* And, as the body of the rate monotonic scheduling theory [Klein et al., 1993, Lehoczky et al., 1989] stands to demonstrate, provable predictions can be routinely obtained for preemptively scheduled systems.

The acquisition of such a glaring evidence, though, is not yet seemingly in sight for the space domain; quite possibly because of the notorious 8-year delay which apparently takes for ground technology to reach and penetrate the space market (cf. [ESA, 1995b]).

It is clear, therefore, that the introduction of the proposed development model shall have to overcome not only the known *technical difficulties* associated with the use of fixed priority preemptive scheduling (e.g.: more demanding run-time environment and potential pessimism incurred with the worst-case scheduling analysis techniques required to prove the predictability of the system) but also the *cultural barriers* which continue to deny all forms of non-deterministic concurrency in general, and Ada tasking in particular, any possibility of utilisation in critical

components of space systems.

# 4.4 HRT-HOOD as the Centre of the Development Process

The HRT-HOOD method [Burns and Wellings, 1994, Burns and Wellings, 1995b] was defined by the Real-Time Group at the University of York (England) in the frame of a study programme initiated by the European Space Agency with the aim to devise ways to improve the productivity of HOOD and Ada technology in the construction of new-generation real-time on-board systems. The author of this technical report actively participated in the project and the main lessons learned from the programme (which are summarised in [British Aerospace, 1993]) provided the main direction to the definition of the proposal discussed in this technical report.

It is not the intent of this technical report to provide an exhaustive presentation of the method. The interested reader is referred to the relevant literature, in particular [Burns and Wellings, 1994] and [Burns and Wellings, 1995b]. In the following, we shall only concentrate on the features which are specifically relevant to the operation of the proposed concept.

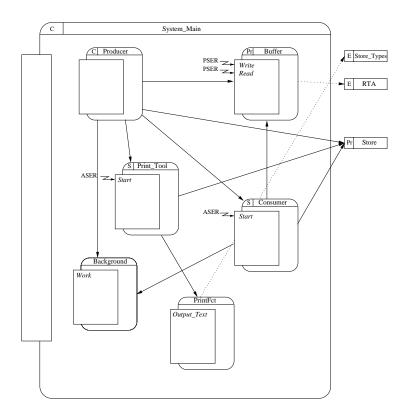

The central goal of the method was to amend the base HOOD method with all of the additions and constraints deemed necessary to ensure that the design can be statically analysed for its timing characteristics at all stages of development.

To this end, and in recognition of the requirements discussed in chapter 1 and 3, the definition of the HRT-HOOD method was geared towards the following objectives:

- 1. to promote *evolutionary* enhancements to the base HOOD method that would not break but retain the principles of the base method;

- to establish explicit and direct bindings between the constructs, concepts and constraints of design and a definite instance of Computational Model based on the revised form of the Ada 95 tasking model;

- 3. to instigate the conduction of an iterative design process prompted by the feedback information obtained from static analysis of the real-time properties of the system.

In keeping with the mandated *evolutionary* approach, the HRT-HOOD method bases its root in HOOD [HTG, 1993] (the main features of which have been briefly presented in section 3.2.2) and enhances it along the following dimensions:

- recognition of the *type* (e.g.: periodic, sporadic, protected) and *criticality* (e.g.: hard, soft, non-critical) of the typical real-time control activities of the application domain

- characterisation of the *real-time requirements* (e.g.: period, offset, deadline) set on such activities

- definition, utilisation and enforcement of those design devices (e.g.: object cooperation exclusively via protected data structures so as to ensure boundedness of blocking) which comply with the rules, properties and constraints set out by the chosen Computational Model for the sake of resulting in a statically analysable design.

Building on the programming abstractions supported by Ada 95 [ISO, 1995], the HRT-HOOD method retains the **passive** object exactly as defined in HOOD; amends the definition of the **active** object by differentiating between:

- cyclic objects, which denote active objects used to model periodic activities

- sporadic objects, which denote active objects used to model event-triggered sporadic activities;

and introduces the **protected** object to denote those objects which provide protected access to shared data structures. In line with the corresponding language abstraction, protected objects (similarly to HOOD active objects) have control over when their invoked operations are executed, but (unlike active objects) need not have any independent thread of control.

While retaining all of the HOOD standard execution requests described in section 3.2.2, HRT-HOOD also supports the following two additional constrained operations on protected objects which ensure mutually exclusive access to the protected data required by the operation:

**protected synchronous (PSER)**: when control flow in the client is interrupted until completion of the protected operation; PSER operations can be state-constrained.

**protected asynchronous (PAER)**: when control flow in the client is interrupted only until the execution request has been received (along with any required input parameters) and acknowledged by the protected object; PAER operations cannot be state-constrained.

Protected objects can also provide any number of unconstrained operations.

Cyclic and sporadic objects may support execution requests for asynchronous transfer of control (ATC) which is intended to allow for other objects in the system to command the immediate termination of the current operation of the object. ATC operations are asynchronous only and are named ASATC for short.

Sporadic objects must also provide for the execution request which is to trigger their sporadic operation. This execution request is modelled by an unconstrained START operation. On the whole, therefore, cyclic terminal objects may *solely and optionally* provide for an ASATC operation, whereas sporadic terminal objects may *optionally* provide for an ASATC operation and *compulsorily* for a START operation.

HRT-HOOD disallows the "use" relationships which would cause objects to incur unbounded blocking or arbitrary synchronisation. Furthermore, in keeping with the hierarchical object-based nature of the HOOD method and in order to allow non-terminal active objects to be meaningfully marked as cyclic, sporadic and protected, HRT-HOOD introduces some restrictions on the allowable parent-child relationships so that the type properties of the parent object are not violated by any of its child objects. The relevant prescriptions are shown in table 4.2 and 4.3.

Table 4.2 shows that, while retaining the HOOD requirement that passive parent objects must *solely* decompose to other passive child objects, HRT-HOOD adds the corresponding prescription that protected parent objects *cannot* decompose to cyclic nor sporadic child objects as the properties of the latter are incompatible with that of the former.

Table 4.2: Disallowed "Implemented By" Relationships.

Table 4.3 shows that passive objects can *only* use the operations of other passive objects whereas protected objects can call operations of any other active (meaning cyclic, sporadic or protected) objects *so long as* they are unconstrained (which ensures that their execution time can be bounded).

On the whole, HRT-HOOD objects are described by: their provided operations; their threads of control; their synchronisation requirements; and the real-time requirements set on their operations (i.e. criticality, period — or interarrival time —, deadline, WCET and priority).

Criticality, period and deadline are *user-assigned* design attributes and are expected to change only as a result of a design change. Conversely, WCET and priority are *computed* properties; the former may vary with the progress of the development (i.e. from a best-guess prediction, made at a very early stage of design, to the value returned from WCET analysis against the final code); the latter is calculated by the schedulability analysis tool based on the user-assigned criticality and deadline of the object in question.

So long as the user maintains the design information current with the progress of the implementation, the semantic contents of an HRT-HOOD design is such that the associated analysis tools permit to constantly verify its feasibility in the time domain and, accordingly, derive the feedback necessary to steer the design and implementation to completion.

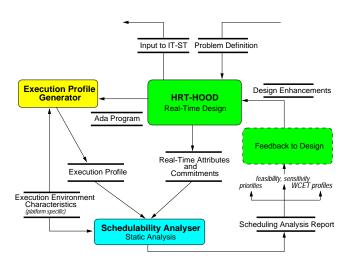

Figure 4.4 depicts the instantiation of the abstract process model shown in figure 4.2 that we have constructed around HRT-HOOD.

The figure places emphasis on the iterative nature of the development flow we want to support. In our concept, such iterations represent incremental stages of development supported by various forms of feedback information. Static analysis constitutes our primary source of feed-

| Tuesto ties i i i i i i i i i i i i i i i i i i |        |              |               |         |

|-------------------------------------------------|--------|--------------|---------------|---------|

| USED                                            | cyclic | sporadic     | protected     | passive |

| User                                            |        |              |               |         |

| cyclic                                          |        |              |               |         |

| sporadic                                        |        |              |               |         |

| protected                                       | ASATC  | ASATC, START | unconstrained |         |

| passive                                         | X      | X            | X             |         |

Table 4.3: Allowed & Disallowed "Use" Relationships

Figure 4.4: Design Activities in Operation.

back. The figure shows the main components of the feedback from static analysis, that is: (1) the confirmation of the *schedulability* of the individual threads of the system with respect to the relevant real-time requirements; and (2) the *sensitivity* of the system timeliness to variations in the processing requirements of individual threads.

Notably, the implementation of an HRT-HOOD design aid tool supporting *all* of the data paths shown in figure 4.4 has recently been completed [Intecs Sistemi, 1996a] and successfully demonstrated. The dashed rectangle in the figure depicts the sole stage of the process which is *not* assisted by automated tools and relies upon the engineering authority's interpretation of the results obtained from static analysis.

In the following, we describe the key technology elements which are required to enable the effective operation of our process model.

# 4.5 Enabling Technology

# 4.5.1 The HRT-HOOD Computational Model

HRT-HOOD [Burns and Wellings, 1994, Burns and Wellings, 1995b] extends the base HOOD method by incorporating the abstractions supported by the revised tasking model of Ada 95 [ISO, 1995]. As a reflection of that, the HRT-HOOD Computational Model is based around the principles of fixed priority preemptive scheduling described earlier in section 3.4.5. Moreover, our implementation of the HRT-HOOD Computational Model places in perfect match with the tasking profile identified at the 8th International Real-Time Ada Workshop as the most suitable candidate for the support of concurrent time-critical applications [Baker and Vardanega, 1997] and referred to as the 'Ravenscar profile'.

Systems designed with the HRT-HOOD method are concurrent and provided with a direct mapping to the corresponding concurrency constructs at the language level. In particular, as outlined in section 4.4, the HRT-HOOD Computational Model:

- 1. retains the *passive* object exactly as defined in HOOD (i.e. an entity which has no internal concurrency and no control over when its invoked operations are executed);

- 2. amends the HOOD definition of *active* object (corresponding to an entity with internal concurrency and control over when its invoked operations are executed) by differentiating between:

- cyclic objects, which denote active objects used to model time-triggered activities;

and

- sporadic objects, which denote active objects used to model event-triggered activities;

and, finally,

introduces the protected object to denote those objects which provide protected access to shared data structures.

HRT-HOOD active objects are threaded and possess a well-defined mapping to one particular instance of the basic unit of concurrency of the Ada language (i.e. the task). Conversely, protected objects resemble active objects in so far as having control over when their invoked operations are executed, but, unlike them and in accordance with the corresponding language abstraction, need no independent thread of control.

The HRT-HOOD Computational Model requires that the threads of control associated with active objects abide by the following rules:

- threads may access shared data in a protected manner by means of mutually exclusive calls to dedicated *resource* servers, which are modelled as HRT-HOOD protected object;

- resource servers may offer a variety of services, each denoted by one distinct execution request; the execution requests exported by a resource server must ensure mutual exclusion to concurrent callers and must be internally non-blocking (i.e. allow no functional activation constraints nor perform blocking calls, for either would render static analysis impossible);

- threads may synchronise with one another by means of mutually exclusive calls to dedicated *synchronisation* servers;

- synchronisation servers allow threads to suspend on synchronisation calls and other threads to perform non-blocking triggering calls; the model requires that any thread which wishes to suspend on a synchronisation call be allowed to do so exclusively through the services of a dedicated synchronisation server. (In other words, no two threads can suspend on one and the same synchronisation call so that no suspension queue be required for any synchronisation service.)

HOOD objects are defined by the service they provide for use by other objects. The provided service is specified in the *interface* of the object. The control behaviour of the object with respect to the execution requests received at the interface is described in the *object control structure* (OBCS). The relevant services are implemented by a set of *operation control procedures* (OPCS). HRT-HOOD retains these base principles and maps the resulting entities on to the abstractions supported by the Computational Model we have just described.

Cyclic objects do not provide external operations that can be invoked by other objects, except for those which request the termination of the current operation of the object or the reset (e.g.: mode change) of its service status. Accordingly, the cyclic object is implemented by a maximum of two cooperating entities, as follows:

- the *thread*, which is to perform the time-triggered operation of the object and maps to an independent thread of control implemented as an *entry-less* Ada task with a single, time-triggered invocation event and a potentially unbounded number of invocations; and

- the *OBCS*, which is needed only if the object is required to support execution requests associated with termination or reset operations. The communication between the cyclic thread and its OBCS can be asynchronous (and, therefore, implemented as an Ada 95 asynchronous transfer of control operation initiated by the OBCS and taking effect in the thread) or synchronous (and, consequently, implemented as a synchronous status enquiry performed by the thread towards the OBCS). In the latter case (which is, in fact, the preferred one) the OBCS of the cyclic object naturally maps to a *resource server*.

Sporadic objects do always support at least one execution request, which triggers the sporadic operation of the object. The triggering event may be *external* (i.e. an interrupt) or *internal* (i.e. on demand from another software object in the system). The object triggered by the former type of execution request is called *interrupt sporadic*; the object triggered by the latter, *software sporadic*. Similarly to cyclic objects, sporadic objects may also provide additional execution requests for termination or reset operations.

The *software sporadic* object is modelled by a maximum of two cooperating entities, as follows:

- the thread in charge of the sporadic operation of the object, which maps to an independent thread of control implemented as an entry-less Ada task with a single, event-triggered invocation event and a potentially unbounded number of invocations; and

- the OBCS, which is to receive the execution requests arriving from other objects in the

system and dispatch them to the sporadic thread. The triggering event is transferred from

the OBCS to its software sporadic thread as the release from a dedicated synchronisation

call. All other communications follow the model described for the cyclic object. As a

result of that, the OBCS of the software sporadic object naturally maps to a synchronisation

server.

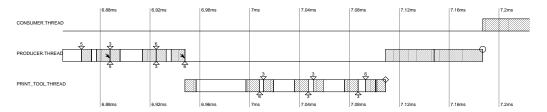

Figure 4.5 portrays a simplified view of the task templates required to model the cyclic thread, the software sporadic thread along with its OBCS (synchronisation server).

```

entry Wait (<params>);

procedure Signal (<params>);

end OBCS;

task Cyclic is

pragma priority (<value>);

end Cyclic;

protected body OBCS is

-- local variables

entry Wait (<params>)

task Software_Sporadic is

pragma priority (<value>)

end Software_Sporadic;

task body Cyclic is

when (Barrier) is

local variables

task body Software_Sporadic is

begin

-- release actions

begin

local variables

- set time reference T

begin

raise barrier

main loop external set up

end Wait;

loop

delay until T;

procedure Signal (<params>) is

OBCS.Wait (<params>);

-- periodic action

T := T + Period;

begin

- lower barrier

-- sporadic action

end loon:

end loop;

end Signal;

end Cyclic

end Software_Sporadic;

```

protected OBCS is

Figure 4.5: Task Templates.

This modelling paradigm does not necessarily hold for the implementation of the *interrupt sporadic* object, as the service it provides is typically immediate and short-lived and, hence, has no use for termination operations while having an implicit (hardware) caller for the triggering operation. Depending on the support provided by the underlying implementation language, the interrupt sporadic object may map to an interrupt task (like in Ada 83) or a protected interrupt procedure (like in Ada 95).

Whereas interrupt sporadic objects are a powerful aid for the designer to explicitly model the service associated with the arrival of external interrupts (which are an essential ingredient of any real-time embedded system) software sporadic objects represent a very flexible tool to express and model *precedence activation constraints* between concurrent activities. As discussed in chapter 2, in fact, precedence activation constraints frequently arise between several of the data processing functions which are performed on board. In particular, intelligent use of software sporadic objects, in conjunction with suitable assignment of software priorities, caters for the achievement of the *increased responsiveness* and *maximum utilisation of available processing power* requirements discussed in chapter 1 (**R.4** and **R.6** respectively).

### 4.5.2 Ada Implementation

The engineering concept depicted in figure 4.2 was expressly intended to operate with Ada 95 software production factories. However, while awaiting industrial-quality commercial implementations of the language standard, the *current* implementation of the relevant industrial toolset has been realised upon an existing Ada 83 technology baseline augmented by the introduction of a limited number of upward-compatible enhancements. Implementations of the proposed concept based on actual Ada 95 technology will be realised as soon as mature technology becomes available. (Attractive concept demonstrators may possibly be implemented by integration of such handy technology as GNAT [Ada Core Technologies, 1996] and STAMP [Chapman et al., 1996].)

Implementation of the HRT-HOOD Computational Model on Ada 83 technology requires the following distinct forward-compatible enhancements:

- a large range of software priorities ( $\geq 64$ );

- the concept of passive task with similar semantics to the protected type of the Ada 95 language standard [ISO, 1995];

- the concept of *absolute* delay to permit jitterless modeling of periodic tasks;

- the concept of *monotonic* time to avoid the overhead of the time-of-day based clock handling.

Our Ada implementation was targeted to the 32-bit Embedded Real-Time Computing Core (ERC32) [Gaisler, 1994, ESA, 1992a, Saab Ericsson Space, 1997], a SPARC v7 based chipset inclusive of Integer Unit, Floating Point Unit and Memory Controller, intended for use in *no-cache no-virtual memory* single-board computers for advanced new-generation on-board systems. Amongst other features, which are not discussed in this technical report, the ERC32 chipset and associated Ada compilation system optionally supports board configurations which include the ATAC (Ada Tasking Coprocessor) chip [Roos and Gomez-Molinero, 1992]. The ATAC is a memory-mapped hardware device which performs Ada 83 tasking operations on behalf of classical software run-time systems. Reasons of source-level compatibility between systems built for configurations with or without the ATAC dictated the use of Ada 83 interrupt tasks to model interrupt sporadic objects.

We have recalled earlier in section 4.2.3 that our notion of Computational Model entails the definition and the timing characterisation of the concurrency management mechanisms used at run time for the execution of the system.

In the following, we provide a brief description of the tasking primitives which contribute to the determination of the run-time scheduling behaviour of systems built in accordance with the HRT-HOOD Computational Model. Subsequently, we provide a timing bound for the execution of those primitives on our reference target platform. This shows that the run-time system required to support the HRT-HOOD Computational Model is actually small, compact and fully characterised.

Cyclic tasks call primitive Delay Until to command the time of their next release and the wake-up system uses an Interval Timer instead of the conventional periodic clock. The overall worst-case execution time of the primitive results from the sum of two values: the placement of the task control structure in the interval time queue (*Delay Until(Enter)*) and the return from the call upon release (*Delay Until(Exit)*).

Interrupts off the Interval Timer are serviced by primitive *Timer\_Int*. Primitive *Ready* changes the released cyclic tasks' status to ready. On modifications to the ready status list, primitive *Select* is invoked to determine the "best-task-out"; this may incur preemptive switch to a new running task, which is performed by primitive *Switch*.

Primitive *Int\_Handling* initiates an interrupt accept statement in the body of the designated interrupt sporadic task, while *Int\_Wait(Enter)* and *Int\_Wait(Exit)* allow control to respectively enter and leave the interrupt accept body.

*PO\_Entry* and *PO\_Exit* control respectively the access to and the release of server tasks and include the relevant raising and lowering of the caller's priority.

The implementation of the blocking call to synchronisation servers uses a primitive semaphore structure: the software sporadic task's call to the server's guarded entry translates into the caller's suspension on the primitive semaphore (*Sem.Wait(Enter)*). Arrival of the releasing call causes the suspended task to be freed from the semaphore's queue (*Entry\_Queue\_Mgmt* (which includes the call to *Sem.Signal*) exit from the suspensive call (*Sem.Wait(Exit)*) and potentially become the new running task.

Primitive *Select* involves queue management operations which are typically exposed to pessimistic bounds; the problem was circumvented by redesigning the primitive so as to preserve minimal execution time and also achieve low worst-case bounds. The design restriction of having at most one software sporadic task wait on any given synchronisation server's semaphore queue allows all of the relevant primitive operations to be easily bounded. All the other primitives in the list exhibit deterministic execution time bounds. The characterisation of all such bounds on execution on the selected platform is stored in the so-called *run-time system characteristics file*.

Table 4.4: Timing Characteristics of Basic Run-Time System Primitives ( $\mu$ s).

| Para P. 1.11                | Hand by / for               | DEM32 (10 MHz 0 Wait-states) |               |  |

|-----------------------------|-----------------------------|------------------------------|---------------|--|

| RTS Primitive               | Used by / for               | non-ATAC run-time            | ATAC run-time |  |

| PO_Entry                    | cyclic, sporadic, interrupt | 8.0                          | 13.8          |  |

| PO_Exit                     | cyclic, sporadic, interrupt | 11.0                         | 11.0          |  |

| Int_Wait (Enter)            | interrupt                   | 3.0                          | 3.0           |  |

| Int_Wait (Exit)             | interrupt                   | 3.0                          | 0.0           |  |

| Sem.Wait (Enter)            | sporadic                    | 7.0                          | 7.0           |  |

| Sem.Wait (Exit)             | sporadic                    | 3.0                          | 3.0           |  |

| Entry_Queue_Mgmt            | sporadic                    | 6.0                          | 8.0           |  |

| Select                      | cyclic, sporadic, interrupt | 5.0                          | 0.0           |  |

| Switch                      | cyclic, sporadic, interrupt | 34.0                         | 41.0          |  |

| Delay Until (Insert at Top) | cyclic                      | 39.0                         | 23.0          |  |

| Delay Until (Insert Lower)  | cyclic                      | $22.0 + \mathbf{C} * 3.0$    | 23.0          |  |

| Delay Until (Exit)          | cyclic                      | 8.0                          | 8.0           |  |

| Timer_Int                   | cyclic                      | 21.0                         | 0.0           |  |

| Ready                       | cyclic                      | 12.0                         | 0.0           |  |

| Int_Handling                | interrupt                   | 67.0                         | 0.0           |  |

| Max_Deferred_Preemption     |                             | 130.0                        | 65.0          |  |

Table 4.4 displays the results of a preliminary characterisation of the execution cost of the tasking primitives in our Ada run-time system. The measurements were performed on an ERC32 demonstration board upon completion of the implementation of the relevant Ada technology. The measurements were taken on board configurations with as well as without the ATAC and included the determination of the longest deferred-preemption time incurred during run-time system operation; as it will be explained in section 4.5.3, in fact, that value contributes to the determination of blocking overhead. The table also indicates the correspondence between the tasks in our Computational Model and the run-time primitives required to support them. (Note that the term "sporadic" in the table denotes the software sporadic task, whereas the interrupt sporadic task is denoted by the term "interrupt".)

All expressions in table 4.4 are constant except for the one which describes the cost of placing

a cyclic thread in the delay queue at a position lower than the top in the non-ATAC version of the system. The actual position depends on the relative ordering of the required awake time by the Interval Timer. Term **C**, thus, denotes the total number of cyclic threads currently placed ahead of the presently suspending thread. The best value for **C**, for use by static analysis, obviously depends on the knowledge available to the tool in question. In the case of our analysis model, this value is defaulted to the *total* number of cyclic threads in the system. Conversely, in the ATAC version of the system, this value remains constant as the thread queuing is taken care of entirely by the ATAC chip itself.

## 4.5.3 Static Analysis

The key asset of the engineering approach shown in figure 4.2 lies in the ability to support the design and implementation of a system which can be statically analysed for its real-time characteristics *at all stages of development*. We have claimed earlier in this chapter that this ability descends from the adoption of the notion of Computational Model as the "driving force" of the design process. We now want to present the constructive elements of our approach to static analysis and the way these provisions feed the iterative and incremental component of our development strategy.

### Foundations of Response Time Analysis

The static analysis model chosen for our engineering concept aims at the prediction of worst-case response times (cf. e.g.: [Joseph and Pandia, 1986, Audsley et al., 1993]). The model stipulates that one thread's worst-case response time be defined as the longest elapsed time it takes for that thread to complete its most demanding set of activities in response to an activation occurring under maximum contention from the rest of the system. (The term thread is used in the following as a synonym for task.) The worst-case response time of any thread  $\tau_i$  does, thus, result from suitable combination of the following three distinct components:

- (i) The worst-case computation time of thread  $\tau_i$ , WCCT<sub>i</sub>, which is defined as the sum of the time cost of all  $\tau_i$ 's sequential blocks of execution which lay in the statically determined worst-case path enclosed within the thread's main loop (the thread's execution profile) in addition to the time cost of the run-time system services required for the support of that execution.

- (ii) The *interference* incurred by  $\tau_i$ ,  $\mathbf{I}_i$ , which is caused by the occurrence of preemptive execution of higher-priority threads and higher-priority run-time system services incurred during  $\tau_i$ 's ready period; in the HRT-HOOD Computational Model, the interference incurred from runtime system operation is limited to the handling of the interrupts off the Interval Timer. All other interrupts are, in fact, tied to the activation and execution of interrupt sporadic tasks and, therefore, contribute to the response time of the relevant task.

- (iii) The *blocking* experienced by  $\tau_i$ ,  $\mathbf{B}_i$ , which originates from the possibility that a due release of  $\tau_i$  be delayed by other effects than those arising from preemptive interference; such effects occur when the run-time system protects the execution of internal critical sections by temporarily inhibiting (i.e. deferring) preemption as well as a consequence of using *priority ceiling emulation* for the implementation of mutual exclusion in the communications between tasks and

servers; use of priority ceiling emulation may, in fact, delay the release of tasks whose priority is higher than the caller but lower than the server's ceiling; response time analysis prescribes that worst-case blocking be determined as the *largest* possible delay effect incurred from any of the two sources.

For any thread  $\tau_i$ , component  $WCCT_i$  is fully determined at compile time on the Ada closure of the program, component  $\mathbf{B}_i$  is a function of the assigned priorities and the system's run-time performance, and component  $\mathbf{I}_i$  is a function of the system load.

Component  $WCCT_i$  and  $B_i$  are maximised by analysis. Care must be taken, though, to avoid incurring excessive pessimism in their determination, as this may hinder the usefulness of the analysis. The approach taken to the determination of  $B_i$  and the issues in the generation of the worst-case execution profiles from which  $WCCT_i$  is determined are discussed separately in the following.

Component  $I_i$  is maximised by assuming all runs to occur under the notional concept of *critical instant*, whereby:

- all cyclic tasks are assumed to be disjointly released at time  $t_0 = 0$

- all interrupt sporadic tasks are assumed to be disjointly triggered at time  $t_0 = 0$  and arrive at their maximum frequency

- all software sporadic tasks are assumed to be disjointly released off their synchronisation server's queue at time  $t_0 = 0$ .

The formulae which capture the interference effects on  $\tau_i$ 's ready period over the interval [0,t) are shown in the following, where notation  $j\epsilon HP(i)$  denotes that thread  $\tau_j$ 's priority is greater than  $\tau_i$ 's (i.e.  $Pr(\tau_j) \geq Pr(\tau_i)$ ) notation  $j\epsilon LP(i)$  denotes the converse (i.e.  $Pr(\tau_j) < Pr(\tau_i)$ ) and  $T_j$  denotes  $\tau_j$ 's period (for cyclic threads) or minimum interarrival time (for sporadic threads):

### **Interference from Preemptive Execution of Higher-Priority Threads over [0,t)**:

$$\mathbf{I}_{i}^{t} = \sum_{j \in HP(i)} \lceil \frac{t}{T_{j}} \rceil \mathbf{WCCT}_{j}$$

(4.1)

**Interference from Interrupts Off the Interval Timer over [0,t)**:

$$\mathbf{C}_{i}^{t} = \mathbf{K}_{i}^{t} * (Timer\_Int + Ready + Select)$$

$$\tag{4.2}$$

The terms in *italics* in equation 4.2 denote the run-time primitives involved in the readying of a (cyclic) thread off the delay queue. The constant values to use for the resolution of these equation are those listed in table 4.4. Term  $K_i^t$  determines how many times the Interval Timer triggers over the time span under consideration. This number is determined as follows: