| Version 46 (modified by , 3 years ago) ( diff ) |

|---|

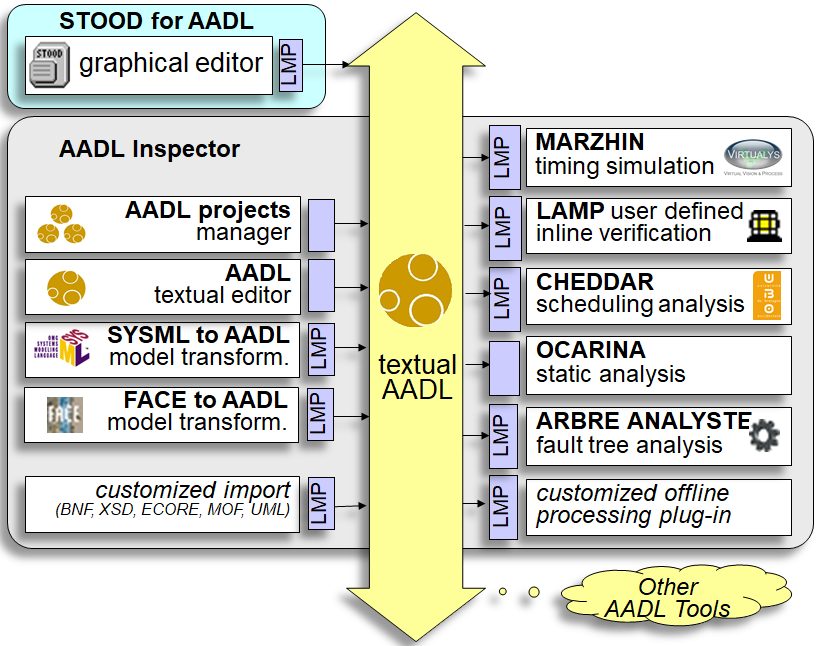

AADL Inspector

AADL Inspector is a model processing framework for Critical Software Architecture Models. Based on the most recent version of the SAE-AS5506 (AADL) standard, it embeds a set of timing analysis, simulation and code generation tools. The tool also provides customizable input model converters for UML profiles or Domain Specific Modelling Languages.

Download the last version of the brochure, the features overview the user manual or ask for a free trial version of the product by sending an email to aadl@ellidiss.fr

The current version of AADL Inspector (v1.8) encompasses the following features:

- Import of AADL textual specifications (individual files or projects)

- Syntactic analysis (aadlrev)

- AADL v2.2 (AS-5506C)

- AADL Behavior Annex v2.0 (AS-5506/2A Annex D)

- AADL Error Model Annex v2.0 (AS-5506/1A Annex E)

- AADL ARINC 653 Annex (AS-5506/1A Annex A)

- AADL FACE 3.0TM Annex (AS-5506/4 Annex F)

- AADL v1, v2.0 and v2.1 upwards compatibility

- Converts older AADL models into v2.2 (with a few restrictions on property associations)

- Import of UML/MARTE, SysML or Capella models (experimental)

- Import of AADL libraries from GitHub

- AADL template models:

- Multi tasks (Real-Time Scheduling)

- Multi partitions (Time and Space Partitioning)

- Multi processors (Network Communication)

- Multi cores (Partitioned Scheduling)

- Static rules analysis plugins

- Assurance cases online verification

- Logical AADL Model Processing (LAMP) online prolog engine

- Predefined libraries to access AADL model entities

- LAMP Annexes in AADL packages (verification rules)

- LAMP Annexes in AADL components (verification goals)

- Schedulability analysis

- Turnkey integration of the CHEDDAR v3 analysis kernel

- AADL to Cheddar model transformation

- Enhanced output format for post-processing

- VCD (Value Change Dump) file output of the scheduling static simulation

- Response time analysis

- Safety analysis

- Generation of Open PSA file from EMV2

- Fault Tree Analysis with Arbre Analiste

- Dynamic simulation

- Turnkey integration of the MARZIN v2 Multi-Agents simulation engine, developed in collaboration with Virtualys.

- Emulation of the AADL run-time (multi-core, multi-processor and multi-partition architectures)

- Display of dynamic time-lines for Processors, Buses, Processes, Threads and Shared Data

- Asynchronous user interaction: in and out events and data

- Simulation scenarios (input ports) and probes (output ports)

- VCD (Value Change Dump) file output of the simulation trace

- Model Properties spreadsheet

- Extracts main RT properties from all the Thread instances

- Software to Hardware allocation

- Separate configuration files

- PDF documentation generator

- Ada and C code generators (Ocarina)

- Tool customization capabilities

- "plug and check" analysis tools

- Scripting language for plugins definition

- Command line options

- Powered by LMP (Logic Model Processing)

- AADL and XML/XMI parsing

- Model query language

- Model constraints language

- Model transformation language

Attachments (9)

-

LoupeAADL.jpg

(115.4 KB

) - added by 13 years ago.

Loupe AADL

- AI1.8.PNG (258.9 KB ) - added by 3 years ago.

- AI1.8-overview.png (124.8 KB ) - added by 3 years ago.

-

arbre_analyste-2.3.2-win32.zip

(24.2 MB

) - added by 2 years ago.

please refer to: https://www.arbre-analyste.fr/en.html

- inspector9brochure.pdf (1.1 MB ) - added by 11 months ago.

- AI1.9-overview.png (275.1 KB ) - added by 11 months ago.

- AI1.9.PNG (219.6 KB ) - added by 11 months ago.

- AI User Manual.pdf (2.4 MB ) - added by 11 months ago.

- AADLInspector1.9QuickStart.pdf (1.4 MB ) - added by 11 months ago.

Note:

See TracWiki

for help on using the wiki.